## Problem #10 Computer Architecture - Solutions

calculation of 2x-4y:

101000.001

011101.111

$=1.1161111.2^{4} ->1027-1023$

$\Rightarrow E = 1027 = 1024 + 2 + 1$  = 1000000001 5 = 0

F=1101111

> IEEE format 1s:

0 10000000011 110111100...0 4 0 3 DE 0...0

⇒ 403DE00000000000

(b) RNE rounds the result conventionally in those cases in which the contribution from the additional bit positions is either greater than or less than half of an LSB (i.e., rounds up if the contribution from the additional bit positions is more than half of an LSB, and rounds down if the contribution from the additional bit positions is less than half of an LSB).

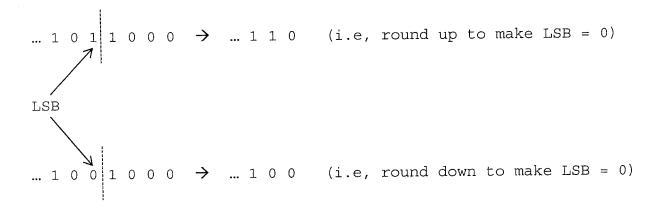

In the special case where the contribution from the additional bit positions is exactly half of an LSB, RNE rounds in such a way as to make the LSB = 0. Two examples are as follows:

Therefore, on average, in those cases where the contribution from the additional bits is exactly half of an LSB, the result will be rounded up or rounded down approximately the same number of times. This means that the rounding procedure will be essentially free of any inherent bias.

(c) This cache has 8 sets (numbered 0 through 7), and each set contains 8 slots.

Note the following about the specific addresses listed:

- (i) All of the even-numbered addresses are mapped into set 6, since they each have a remainder of 6 when divided by 8.

- (ii) All of the odd-numbered addresses (except for 33) are mapped into set 5, since they each have a remainder of 5 when divided by 8.

- (iii) Address 33 is mapped into set 1, since it has a remainder of 1 when divided by 8.

The hits and misses, as well as the final cache contents, are shown on the following page.

| 30 PMF & S               |

|--------------------------|

| _                        |

| 86-miss                  |

| 53- miss                 |

| 61- miss                 |

| 29-miss                  |

| 37-miss                  |

| 30-hit                   |

| 45-miss                  |

| 6-miss                   |

| 22-miss                  |

| 14-miss                  |

| 6-hit                    |

| 53-hit                   |

| 29-hit                   |

| 78-miss                  |

| 22-hit                   |

| 70-miss                  |

| 61-hit                   |

| 54-miss                  |

| •                        |

| 62-miss<br>(replaces 86) |

| (replaces 86)<br>45-hit  |

| 30-hit                   |

| 21-miss                  |

| 77- miss                 |

| • •                      |

| 85-miss                  |

| 46-miss                  |

| (replaces 14)            |

| 33 -miss                 |

| set | address                                                                                                    |

|-----|------------------------------------------------------------------------------------------------------------|

| 0   | (not used)                                                                                                 |

| 1   | 33                                                                                                         |

| 2   | (not used)                                                                                                 |

| 3   | (not used)                                                                                                 |

| 4   | (not used)                                                                                                 |

| 5   | <ul> <li>63</li> <li>61</li> <li>29</li> <li>37</li> <li>45</li> <li>21</li> <li>77</li> <li>85</li> </ul> |

| 6   | 30<br>86 621<br>6<br>22<br>14 46<br>78<br>70<br>54                                                         |

| 7   | (not used)                                                                                                 |

5B 00 00 37

0101 1011 0000 ... 0011 0111 LDT r12 , #55

13 59 00 3F

0001 0011 0101 1001 0-- 0011 1111 5UB r13, r12, #63

13 DA 60 00

0001 0011 1101 1010 0110 0 ... 0 SUB r15, r13, r12

F8 00 00 00

1111 1000 0 --- 0 HLT

LDI 112, #55 Instruction #1: C=x V=x Z=x N=xCondition codes: 00000037 xxxxxxxx xxxxxxx xxxxxxx R[12 - 15]: SUB rl3/rl2/#63 C=1 V=0 Z=0 N=1 Instruction #2: Condition codes: 00000037 fffffff8 xxxxxxxx xxxxxxx R[12 - 15]:SUB r15, r13, r12 Instruction #3: Condition codes: C=0 V=0 Z=0 N=1R[12 - 15]:00000037 fffffff8 xxxxxxxx ffffffc1 Instruction #4: HLTCondition codes: C=0 V=0 Z=0 N=1R[12 - 15]:00000037 fffffff8 xxxxxxxx ffffffc1