| Title:             | Scaling Limits of Programmable Fluidic Self-Assembly Forming<br>Electrical Interconnects |

|--------------------|------------------------------------------------------------------------------------------|

| Award Number:      | 822202                                                                                   |

| PI:                | Prof. Heiko O. Jacobs, University of Minnesota                                           |

| Graduate Students: | Robert Knuesel, Se-Chul Park, Michael Motala                                             |

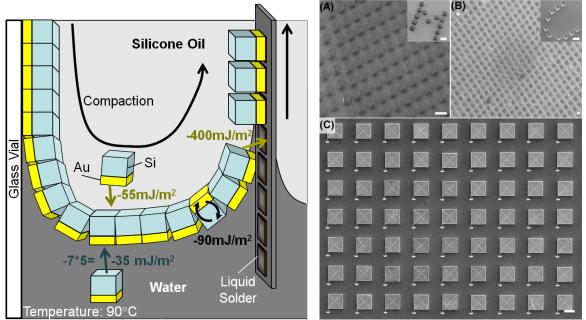

Fig. 1 Novel triple-interface-based self-assembly method, as well as resulting SU-8 and silicon component assembly on rigid and flexible substrates.

Progress in the fields of microelectronics and microoptics has traditionally been measured by the overall level of miniaturization. The emerging field of macro and printable electronics, however, has a different set of goals and draws attention to new manufacturing methods that enable large-area integration, preferably on flexible low temperature plastic substrates. Directed/engineered self-assembly is uniquely suited as a mechanism to enable such fabrication. This methodology allows for the redistribution of components over large areas and the ordering of unorganized parts. For example, a container full of semiconductor dies/chiplets can be redistributed and assembled at precise locations on a substrate at any desired pitch or required function density using methods of directed self-assembly. Interestingly, the minimal component size for high yield assemblies of electronic components has been limited to >100  $\mu$ m sized chiplets using current methods primarily since gravity driven sedimentation used to introduce the components to the substrate has not been effective at the <100  $\mu$ m length scale. Gravitational forces scale with the volume and are ineffective in delivering highly scaled components, which remain suspended in solution during agitation. These components are orders of magnitude smaller than current state of the art considering serial robotic pick and place. In a broader sense, the ability to localize arbitrary materials and devices on arbitrary substrates allows the merging of technologies based on otherwise incompatible materials.

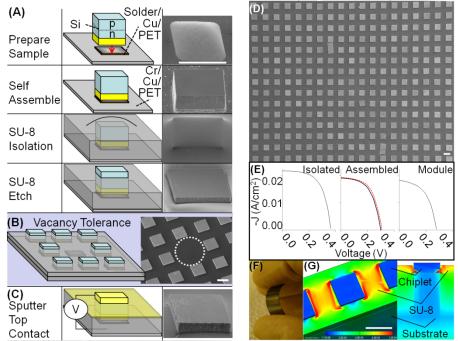

Professor Heiko O. Jacobs and his research group at the University of Minnesota have been developing a process to integrate functional semiconducting devices across length scales and material boundaries in a parallel manner. The first objective is to enable chip level selfassembly (currently performed with mm-sized components) at the 10 to 50 µm length scale utilizing surface tension to direct the self-assembly process. This has been accomplished by introducing an entirely new component introduction process which takes place at the triple interface between silicone oil, water, and a penetrating solder-patterned substrate shown in Fig 1 (NSTI-Nanotech Conference, 2007, Materials Research Society Proceedings, 2007, Materials Research Society Proceedings, 2009). The assembly is driven by a stepwise reduction of interfacial free energy where chips are first collected and pre-oriented at an oil-water interface before they assemble on a solder-patterned substrate that is pulled through the interface. Patterned transfer occurs in a progressing linear front as the liquid layers recede. The process eliminates the dependency on gravity and sedimentation of prior methods, thereby extending the minimal chip size to the sub-100 micrometer scale. Figure 1A,B,C depict self assembly results of varying component/substrate materials with non-uniform packing density featuring very high angular orientation accuracy. The second objective, which is to develop a process to assemble components, micro/nanochips to enable "Nano-Flip-Chip-Assembly" with contact pad registration, has first been demonstrated with a fault-tolerant segmented flexible monocrystalline silicon solar cell that reduces the amount of Si that is used when compared to conventional rigid cells (Proceedings Of The National Academy of Sciences of the United States of America, 2010, Proceedings of Foundations of Nanoscience: Self-Assembled Architectures and Devices, 2010.). The process and results can be seen in Fig. 2.

Fig. 2 Fault tolerant, flexible, segmented Si solar cell fabrication process based on self-assembly and results.

The ability to carry out self-assembly across scales lends itself to many future applications including flexible high performance electronics, solar cells, and sensor systems to gather optical, acoustic, chemical, and/or radiological data that would improve many areas of our daily lives including healthcare, the environment, energy, food safety, manufacturing, and national security.

Publications Acknowledging Funding:

Knuesel, RJ; Jacobs, HO. "Self-assembly of microscopic chiplets at a liquid-liquid-solid interface forming a flexible segmented monocrystalline solar cell," *PROCEEDINGS OF THE NATIONAL ACADEMY OF SCIENCES OF THE UNITED STATES OF AMERICA*, v.107, 2010, p. 993-998.

Robert J. Knuesel and Heiko O. Jacobs. "Fluidic Surface-Tension-Directed Self-Assembly of Miniaturized Semiconductor Dies Across Length Scales and 3D Topologies," *â??*, *in Material Systems and Processees for Three-Dimensional Micro- and Nanoscale Fabrication and Lithography Mater. Res. Soc. Symp. BB Proc.* (2009), 2009.

Robert J. Knuesel, Se-Chul Park, and Heiko O. Jacobs. "Self-Packaging and Self-Mounting of Miniaturized Semiconductor Dies Across Length Scales and 3D Topologies," *Proc. Foundations of Nanoscience: Self-Assembled Architectures and Devices (FNANO10), Snowbird, Utah April 27-30*, 2010.